据长江存储CEO杨士宁在IC咖啡首届国际智慧科技产业峰会(ICTech Summit 2017)上介绍,32层3D NAND芯片顺利通过电学特性等各项指标测试,达到预期要求。该款存储器芯片由长江存储与微电子所三维存储器研发中心联合开发,在微电子所三维存储器研发中心主任、长江存储NAND技术研发部项目资深技术总监霍宗亮的带领下,成功实现了工艺器件和电路设计的整套技术验证,向产业化道路迈出具有标志性意义的关键一步。

在大数据需求驱动下,存储器芯片已是电子信息领域占据市场份额最大的集成电路产品。我国在存储器芯片领域长期面临市场需求大而自主知识产权和关键技术缺乏的困境,开展大容量存储技术的研究和相关产品研制迫在眉睫。传统平面型NAND存储器在降低成本的同时面临单元间串扰加剧和单字位成本增加等技术瓶颈。寻求存储技术阶跃性的突破和创新,是发展下一代存储器的主流思路。

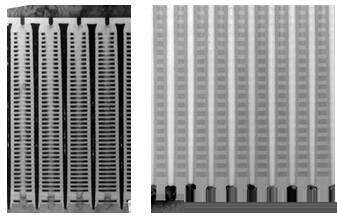

3D NAND是革新性的半导体存储技术,通过增加存储叠层而非缩小器件二维尺寸实现存储密度增长,从而拓宽了存储技术的发展空间,但其结构的高度复杂性给工艺制造带来全新的挑战。经过不懈努力,工艺团队攻克了高深宽比刻蚀、高选择比刻蚀、叠层薄膜沉积、存储层形成、金属栅形成以及双曝光金属线等关键技术难点,为实现多层堆叠结构的3D NAND阵列打下坚实基础。

存储器的可靠性是影响产品品质的重要一环,主要评估特性包括耐久性、数据保持特性、耦合和扰动,国际上在3D NAND领域的公开研究结果十分有限。器件团队通过大量的实验和数据分析,寻找影响各种可靠性特性的关键因素,并和工艺团队紧密协作,完成了器件各项可靠性指标的优化,最终成功实现了全部可靠性参数达标。

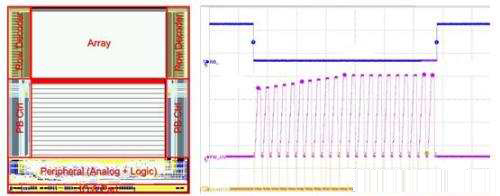

在电路设计层面,堆叠三维阵列的集成研发面临比平面型NAND更复杂的技术问题,需要结合三维器件及阵列结构特点进行分析和优化。设计团队对三维存储结构进行建模,采用根据层数可调制的编程、读取电压配置,补偿了器件特性随阵列物理结构的分布差异,降低了单元串扰影响。并且,应用了诸多创新性的先进设计技术,保证了芯片达到产品级的功能和性能指标。

3D NAND存储器芯片研发系列工作得到了国家集成电路产业基金、紫光控股、湖北省国芯投资、湖北省科投的大力支持。

图1. 3D NAND阵列TEM照片

图2. 芯片版图布局(左),擦除操作测试波形(右)