如今在半导体工艺上,台积电一直十分激进,7nm EUV工艺已经量产,5nm马上就来,3nm也不远了。

台积电CEO兼联席主席蔡力行(C.C. Wei)在投资者与分析师会议上透露,台积电的N3 3nm工艺技术研发非常顺利,已经有早期客户参与进来,与台积电一起进行技术定义,3nm将在未来进一步深化台积电的领导地位。

目前,3nm工艺仍在早期研发阶段,台积电也没有给出任何技术细节,以及性能、功耗指标,比如相比5nm工艺能提升多少,只是说3nm将是一个全新的工艺节点,而不是5nm的改进版。

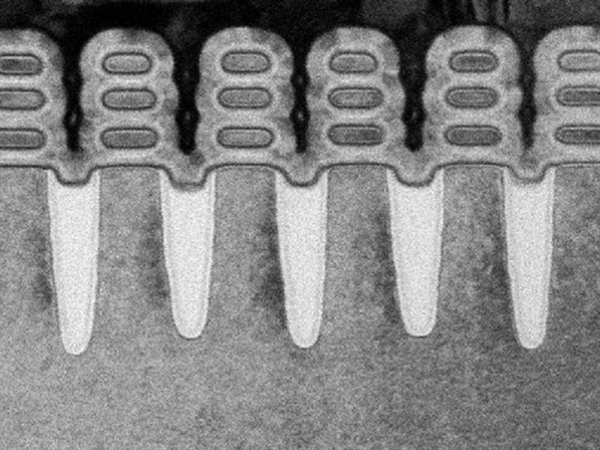

台积电只是说,已经评估了3nm工艺所有可能的晶体管结构设计,并与客户一起得到了非常好的解决方案,具体规范正在进一步开发中,公司有信心满足大客户们的所有要求。

三星此前曾披露,将在3nm工艺上采用基于纳米片(nano-sheet)的环绕式栅极(Gate-All-Around) MBCFET晶体管结构,工艺节点简称3GAAE。

考虑到台积电必须在新工艺上保持足够的竞争力,而且强调过3nm是全新的,所以必然也会有新的架构、技术、材料等。

另外,台积电5nm工艺使用了14个EUV极紫外光刻层,3nm上应该会使用更多,但仍可能继续保留DUV深紫外光刻技术,混合使用。

台积电此前曾披露,计划在2022年就量产3nm工艺。

本站文章版权归原作者所有 内容为作者个人观点 本站只提供参考并不构成任何投资及应用建议。

本文转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。如涉及作品内容、版权和其它问题,请在30日内与本网联系,我们将在第一时间删除内容!